GUIDE TO PROGRAMMING

# GUIDE TO PROGRAMMING

67095664

Copyright Fairchild Camera & Instrument Corp. 1976

Fairchild Micro Systems 1725 Technology Drive, San Jose, CA 95110

# **TABLE OF CONTENTS**

#### SECTION

#### PAGE

| 1.0 | <b>INTR</b><br>1.1<br>1.2 | ASSUM           | ON<br>IED READER BACKGROUND<br>RTING DOCUMENTATION | 1-1<br>1-1<br>1-1 |

|-----|---------------------------|-----------------|----------------------------------------------------|-------------------|

| 2.0 |                           | 8 MICR          | OPROCESSOR SYSTEM                                  | 2-1               |

|     | 2.1                       |                 | S A MICROPROCESSOR                                 | 2-1               |

|     | 2.2                       |                 | BASIC CONCEPTS                                     | 2-1<br>2-1        |

|     |                           | 2.2.1<br>2.2.2  |                                                    | 2-1<br>2-2        |

|     |                           | 2.2.2           | PROGRAMMABLE CLOCKS                                | 2-2               |

|     |                           | 2.2.4           | DIRECT MEMORY ACCESS                               | 2-2               |

|     |                           | 2.2.5           | A COMPLETE MICROPROCESSOR SYSTEM                   | 2-3               |

|     | 2.3                       | THE F8<br>2.3.1 | SYSTEM<br>CHIP AND I/O PORT SELECTION              | 2-4<br>2-4        |

|     | 2.4                       | TUE 20          | 50 CPU                                             | 2-4               |

|     | 2.4                       | 2.4.1           | TIMING                                             | 2-4<br>2-4        |

|     |                           | 2.4.2           | CPU REGISTERS                                      | 2-6               |

|     |                           | 2.4.3           | STATUS                                             | 2-6               |

|     |                           | 2.4.4           | 3850 INPUT/OUTPUT                                  | 2-7               |

|     | 2.5                       | THE 38          | 51 PSU                                             | 2-7               |

|     |                           | 2.5.1           | 3851 TIMING                                        | 2-7               |

|     |                           | 2.5.2<br>2.5.3  | 3851 REGISTERS                                     | 2-8               |

|     |                           | 2.5.3           | 3851 INPUT/OUTPUT                                  | 2-9<br>2-9        |

|     | 0.0                       |                 |                                                    |                   |

|     | 2.6                       | 2.6.1           | 52 DYNAMIC MEMORY INTERFACE                        | 2-9<br>2-9        |

|     |                           | 2.6.2           | 3852 REGISTERS                                     | 2-9               |

|     |                           | 2.6.3           | 3852 DIRECT MEMORY ACCESS AND MEMORY REFRESH       | 2-10              |

|     | - 2.7                     | THE 38          | 53 STATIC MEMORY INTERFACE                         | 2-10              |

|     | 2.8                       | THE 38          | 54 DIRECT MEMORY ACCESS                            | 2-11              |

|     |                           | 2.8.1           | 3854 REGISTERS                                     | 2-11              |

|     |                           | 2.8.2           | DMA CONTROL CODES                                  | 2-12              |

| 3.0 |                           |                 | IS                                                 | 3-1               |

|     | 3.1<br>3.2                |                 | HARTING                                            | 3-1<br>3-1        |

|     | 3.2                       |                 | E AND OBJECT PROGRAMS                              | 3-1               |

| 4.0 |                           |                 | ANGUAGE SYNTAX                                     | 4-1               |

| 4.0 | 4.1                       |                 | CTION TYPES                                        | 4-1               |

|     | <b>T.</b> I               | 4.1.1           | COMMENTS                                           | 4-1               |

|     |                           | 4.1.2           | EXECUTABLE INSTRUCTIONS                            | 4-1               |

|     |                           | 4.1.3           | ASSEMBLER DIRECTIVES                               | 4-1               |

|     | 4.2                       | INSTRU          | CTION FIELDS                                       | 4-1               |

|     |                           | 4.2.1           | LABEL FIELD                                        | 4-1               |

|     |                           | 4.2.2           |                                                    | 4-2               |

|     |                           | 4.2.3<br>4.2.4  | OPERAND FIELD                                      | 4-2<br>4-2        |

|     |                           | 4.2.5           | ALIGNING FIELDS                                    | 4-3               |

|     | 4.3                       |                 | AGE COMPONENTS                                     | 4-4               |

|     | Ŧ. <b>U</b>               | 4.3.1           | VALID CHARACTERS                                   | 4-4<br>4-4        |

|     |                           | 4.3.2           | CONSTANTS                                          | 4-4               |

|     |                           | 4.3.3           | SYMBOLS                                            | 4-5               |

|     |                           | 4.3.4           | EXPRESSIONS                                        | 4-5               |

| 5.0 |                           |                 | DIRECTIVES                                         | 5-1               |

|     | 5.1                       |                 |                                                    | 5-1               |

|     | 5.2                       | DC ~ DI         |                                                    | 5-1               |

# TABLE OF CONTENTS (Cont'd).

#### SECTION

|     | 5.3<br>5.4<br>5.5                        | EJECT – EJECT CURRENT LISTING PAGE.<br>END – END OF ASSEMBLY.<br>EQU – EQUATE A SYMBOL TO A NUMERIC VALUE .<br>5.5.1 A COMPARISON OF THE EQU AND DC DIRECTIVES.                                                                                                         | 5-2<br>5-2                                    |

|-----|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|     | 5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11 | MAXCPU - SPECIFY MAXIMUM CPU TIME<br>ORG - ORIGIN A PROGRAM<br>SYMBOL - ASSEMBLER PROVIDE A SYMBOL TABLE<br>TITLE - PRINT A TITLE AT THE HEAD OF THE ASSEMBLER LISTING<br>XREF - ASSEMBLER PROVIDE A SYMBOL CROSS REFERENCE LISTING<br>WHEN TO USE ASSEMBLER DIRECTIVES | 5-2<br>5-3<br>5-3<br>5-3<br>5-3<br>5-3<br>5-3 |

| 6.0 |                                          | NSTRUCTION SET                                                                                                                                                                                                                                                          | 6-1                                           |

| 0.0 |                                          |                                                                                                                                                                                                                                                                         |                                               |

|     | 6.1                                      | ADC - ADD ACCUMULATOR TO DATA COUNTER                                                                                                                                                                                                                                   | 6-2                                           |

|     | 6.2                                      |                                                                                                                                                                                                                                                                         |                                               |

|     | 6.3                                      | AM – ADD (BINARY) MEMORY TO ACCUMULATOR                                                                                                                                                                                                                                 |                                               |

|     | 6.4                                      | AMD – DECIMAL ADD, MEMORY TO ACCUMULATOR                                                                                                                                                                                                                                |                                               |

|     | 6.5                                      | AS - BINARY ADDITION, SCRATCHPAD MEMORY TO ACCUMULATOR                                                                                                                                                                                                                  |                                               |

|     | 6.6                                      | ASD – DECIMAL ADD, SCRATCHPAD TO ACCUMULATOR                                                                                                                                                                                                                            |                                               |

|     | 6.7                                      | BRANCH INSTRUCTIONS                                                                                                                                                                                                                                                     |                                               |

|     |                                          | 6.7.1 BF - BRANCH PM FALSE                                                                                                                                                                                                                                              |                                               |

|     |                                          | 6.7.2 BT – BRANCH ON TRUE                                                                                                                                                                                                                                               | 6-7                                           |

|     | 6.8                                      | CI – COMPARE IMMEDIATE                                                                                                                                                                                                                                                  | 6-7                                           |

|     | 6.9                                      | CLR – CLEAR ACCUMULATOR.                                                                                                                                                                                                                                                |                                               |

|     | 6.10                                     | CM - COMPARE MEMORY TO ACCUMULATOR                                                                                                                                                                                                                                      |                                               |

|     | 6.11                                     | COM - COMPLEMENT                                                                                                                                                                                                                                                        | 6-8                                           |

|     | 6.12                                     | DCI – LOAD DC IMMEDIATE                                                                                                                                                                                                                                                 |                                               |

|     | 6.13                                     | DI – DISABLE INTERRUPT                                                                                                                                                                                                                                                  | 6-8                                           |

|     | 6.14                                     | DS – DECREMENT SCRATCHPAD CONTENT                                                                                                                                                                                                                                       | 6-8                                           |

|     | 6.15                                     | EI – ENABLE INTERRUPT                                                                                                                                                                                                                                                   |                                               |

|     | 6.16                                     | IN - INPUT LONG ADDRESS.                                                                                                                                                                                                                                                | 6.0                                           |

|     | 6.17                                     | INC - INCREMENT ACCUMULATOR                                                                                                                                                                                                                                             |                                               |

|     | 6.18                                     | INS - INPUT SHORT ADDRESS                                                                                                                                                                                                                                               |                                               |

|     | 6.19                                     | JMP - BRANCH IMMEDIATE                                                                                                                                                                                                                                                  |                                               |

|     | 6.20                                     | LI – LOAD IMMEDIATE                                                                                                                                                                                                                                                     |                                               |

|     | 6.21                                     | LIS - LOAD IMMEDIATE SHORT                                                                                                                                                                                                                                              | 6-10                                          |

|     | 6.22                                     | LISL – LOAD LOWER OCTAL DIGIT OF ISAR.                                                                                                                                                                                                                                  | 6-10                                          |

|     | 6.22                                     | LISU – LOAD UPPER OCTAL DIGIT OF ISAR                                                                                                                                                                                                                                   |                                               |

|     | 6.23                                     | LM – LOAD ACCUMULATOR FROM MEMORY                                                                                                                                                                                                                                       |                                               |

|     | 6.2 <del>4</del>                         | LNK - LINK CARRY TO THE ACCUMULATOR                                                                                                                                                                                                                                     |                                               |

|     | 6.26                                     |                                                                                                                                                                                                                                                                         |                                               |

|     |                                          | LR – LOAD REGISTER<br>NI – AND IMMEDIATE                                                                                                                                                                                                                                |                                               |

|     | 6.28                                     | NM - LOGICAL AND FROM MEMORY.                                                                                                                                                                                                                                           |                                               |

|     | 6.29                                     | NOP - NO OP                                                                                                                                                                                                                                                             |                                               |

|     | 6.30                                     | NS – LOGICAL AND FROM SCRATCHPAD MEMORY                                                                                                                                                                                                                                 | 6-13                                          |

|     |                                          |                                                                                                                                                                                                                                                                         |                                               |

|     | 6.31                                     | OI – OR IMMEDIATE<br>OM – LOGICAL "OR" FROM MEMORY                                                                                                                                                                                                                      | 6-13                                          |

|     | 6.32                                     |                                                                                                                                                                                                                                                                         |                                               |

|     | 6.33<br>6.34                             | OUT – OUTPUT LONG ADDRESS                                                                                                                                                                                                                                               |                                               |

|     |                                          |                                                                                                                                                                                                                                                                         |                                               |

|     | 6.35                                     |                                                                                                                                                                                                                                                                         | 6-14                                          |

|     | 6.36                                     | PK – CALL TO SUBROUTINE DIRECT AND RETURN FROM                                                                                                                                                                                                                          |                                               |

|     | 6 27                                     |                                                                                                                                                                                                                                                                         |                                               |

|     | 6.37                                     |                                                                                                                                                                                                                                                                         |                                               |

|     | 6.38                                     | SL - SHIFT LEFT                                                                                                                                                                                                                                                         |                                               |

|     | 6.39                                     | SR - SHIFT RIGHT                                                                                                                                                                                                                                                        |                                               |

|     | 6.40<br>6.41                             | ST - STORE TO MEMORY                                                                                                                                                                                                                                                    |                                               |

|     | 6.41<br>6.42                             |                                                                                                                                                                                                                                                                         |                                               |

|     | 6.42<br>6.43                             | XI – EXCLUSIVE OR IMMEDIATE<br>XM – EXCLUSIVE OR FROM MEMORY                                                                                                                                                                                                            |                                               |

|     |                                          | XM – EXCLUSIVE OR FROM MEMORY                                                                                                                                                                                                                                           |                                               |

|     | 6.44                                     |                                                                                                                                                                                                                                                                         | 0-16                                          |

# TABLE OF CONTENTS (Cont'd)

| SEC |                           |                                                                        |                                                                                                                                                                                                                                                        | PAGE                            |

|-----|---------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 7.0 | <b>PROG</b><br>7.1        |                                                                        | NG TECHNIQUES<br>JLATING DATA IN THE SCRATCHPAD<br>SIMPLE SCRATCHPAD BUFFER OPERATIONS<br>INCREMENTING UP, AND DECREMENTING DOWN SCRATCHPAD BUFFERS<br>USING SCRATCHPAD REGISTERS AS COUNTERS.<br>USING SCRATCHPAD REGISTERS FOR SHORT DATA OPERATIONS | 7-1<br>7-1<br>7-1<br>7-3<br>7-3 |

|     | 7.2                       | ROM, R<br>7.2.1<br>7.2.2                                               | AM AND DATA TABLES<br>READING DATA OUT OF TABLES IN ROM<br>ACCESSING DATA TABLES IN RAM                                                                                                                                                                | 7-4<br>7-4<br>7-4               |

|     | 7.3                       | SUBROU<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6           | JTINES<br>THE CONCEPT OF A SUBROUTINE<br>SUBROUTINE PROGRAM STEPS<br>SIMPLE SUBROUTINE CALLS AND RETURNS<br>NESTED SUBROUTINES<br>MULTIPLE SUBROUTINE RETURNS.<br>PASSING PARAMETERS                                                                   | 7-8<br>7-12                     |

|     | 7.4                       | MACRO<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4                              | S<br>DEFINING AND USING MACROS<br>MACROS WITH PARAMETERS<br>RULES FOR DEFINING AND USING MACROS<br>WHEN MACROS SHOULD BE USED                                                                                                                          | 7-14<br>7-14<br>7-15            |

|     | 7.5                       | JUMP T<br>7.5.1<br>7.5.2<br>7.5.3                                      | ABLES                                                                                                                                                                                                                                                  | 7-16<br>7-16                    |

|     | 7.6                       | STATUS<br>7.6.1<br>7.6.2                                               | 6, BITS AND BOOLEAN LOGIC                                                                                                                                                                                                                              | 7-17                            |

|     | 7.7                       | POWER                                                                  | ING UP AND STARTING PROGRAM EXECUTION                                                                                                                                                                                                                  | 7-18                            |

| 8.0 | <b>INPUT</b><br>8.1       |                                                                        | JT PROGRAMMING<br>AMMED I/O<br>POLLING ON STATUS<br>DATA, STATUS AND CONTROLS<br>PARALLEL DATA AND CONTROL PORTS                                                                                                                                       | 8-1<br>8-1<br>8-2               |

|     | 8.2                       | INTERRI<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7 | UPT I/O<br>THE INTERRUPT SEQUENCE<br>ENABLING AND DISABLING INTERRUPTS<br>INTERRUPT PRIORITIES<br>PROGRAM RESPONSE TO AN INTERRUPT<br>MAKING 3851 PSU INTERRUPT ADDRESS PROGRAMMABLE<br>SIMPLE I/O INTERRUPTS<br>A SAMPLE PROGRAM                      | 8-3                             |

|     | 8.3                       | LOCAL<br>8.3.1<br>8.3.2<br>8.3.3                                       | TIMERS (PROGRAMMABLE TIMERS)<br>LOCAL TIMER I/O PORTS<br>PROGRAMMING LOCAL TIMERS<br>A PROGRAMMING EXAMPLE - THE TIME OF DAY                                                                                                                           | 8-7<br>8-7<br>8-8<br>8-8        |

|     | 8.4                       | DIRECT<br>8.4.1<br>8.4.2<br>8.4.3                                      | MEMORY ACCESS                                                                                                                                                                                                                                          |                                 |

| 9.0 | <b>PROG</b><br>9.1<br>9.2 | COUNT                                                                  | PTIMIZATION<br>ING CYCLES AND BYTES<br>NTARY OPTIMIZATION TECHNIQUES<br>SCRATCHPAD AND RAM MEMORY<br>IMMEDIATE INSTRUCTIONS                                                                                                                            | 9-1<br>9-1<br>9-1               |

# TABLE OF CONTENTS (Cont'd)

| SECTION    |                         |                                                                                                        | PAGE  |

|------------|-------------------------|--------------------------------------------------------------------------------------------------------|-------|

|            | 9.2.3<br>9.2.4<br>9.2.5 | SHORT INSTRUCTIONS<br>USE OF DS INSTRUCTION TO DECREMENT AND TEST<br>USE OF THE BR7 INSTRUCTION        | . 9-7 |

| 9.3        | PROGR<br>9.3.1<br>9.3.2 | AMMING FOR SPEED OR MEMORY ECONOMY<br>MACROS AND SUBROUTINES<br>TABLE LOOKUPS VERSUS DATA MANIPULATION | . 9-2 |

| 10.0 SOME  | USEFU                   | L PROGRAMS                                                                                             | 10-1  |

| 10.1       | GENER                   | ATING TEXT                                                                                             |       |

|            | 10.1.1                  | SIMPLE AND DEDICATED TEXT PROGRAMS                                                                     | 10-1  |

|            | 10.1.2                  | UNPACKING DECIMAL DIGITS                                                                               |       |

|            | 10.1.3                  | VARIABLE TEXT                                                                                          | 10-1  |

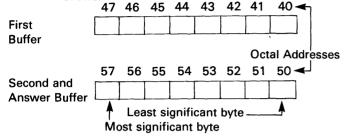

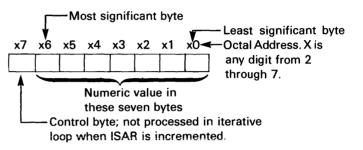

| 10.2       | MULTIB                  | YTE ADDITION AND SUBTRACTION                                                                           | 10-2  |

|            | 10.2.1                  | 16-BIT, BINARY ADDITION AND SUBTRACTION                                                                |       |

|            | 10.2.2                  | MULTIBYTE BINARY OR DECIMAL ADDITION AND SUBTRACTION                                                   |       |

| 10.3       | MULTIP                  | LICATION                                                                                               | 10-3  |

| 10.4       | DI //010                | N                                                                                                      |       |

| 10.4       | DIVISIO                 | N                                                                                                      | 10-5  |

|            | A BIN                   | ARY NUMBER SYSTEM                                                                                      | A-1   |

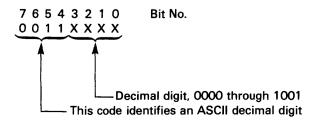

| APPENDIX E |                         | CII CODES                                                                                              |       |

| APPENDIX C |                         | IVERSION TABLES/TIMER COUNTS                                                                           |       |

| APPENDIX D |                         | TRUCTION SUMMARY                                                                                       |       |

|            |                         |                                                                                                        |       |

#### LIST OF ILLUSTRATIONS

#### FIGURE

#### PAGE

PAGE

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9 | Multifunction Logic Device.         Data and Instruction Paths in a Multifunction Logic Device.         Program P Being Interrupted to Execute Program R         Logical Components, Data Paths and Control Paths in any Microprocessor System         F8 Microprocessor System Configurations         Logical Functions of the 3850 CPU         Instruction Timing.         3850 CPU Programmable Registers         Logical Functions of the 3851 PSU | 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-5<br>2-6<br>2-8 |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 2-10<br>2-11<br>2-12                                        | Logical Functions of the 3852 DMI Device<br>Logical Functions of the 3853 SMI Device<br>Logical Functions of the 3854 DMA Device                                                                                                                                                                                                                                                                                                                       | 2-10                                                 |

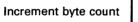

| 3-1                                                         | Flowchart for a Program to Move Data from One RAM Buffer to Another                                                                                                                                                                                                                                                                                                                                                                                    | 3-1                                                  |

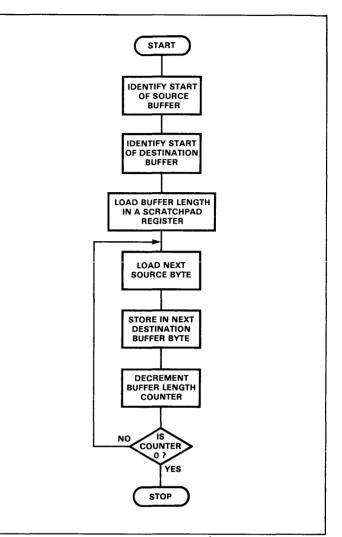

| 3-2                                                         | Flowchart for Program to Add Two Multibyte Numbers and Output the Result                                                                                                                                                                                                                                                                                                                                                                               | 3-2                                                  |

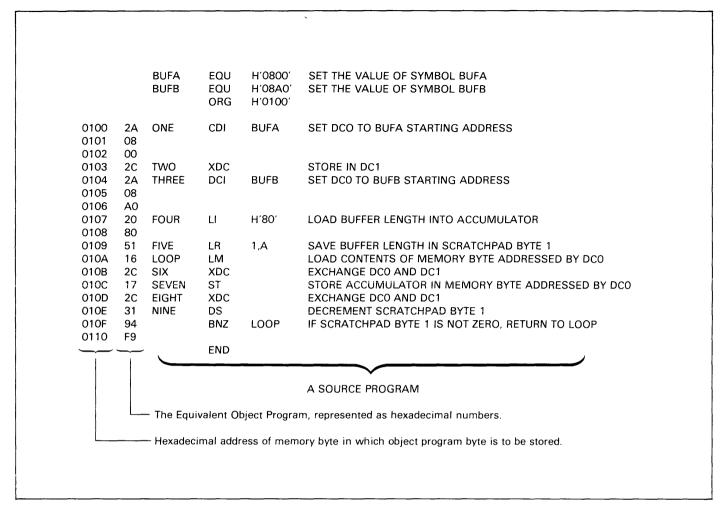

| 3-3                                                         | Source and Object Programs                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-3                                                  |

| 4-1                                                         | Four Comment Lines (Shaded) in a Source Program                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1                                                  |

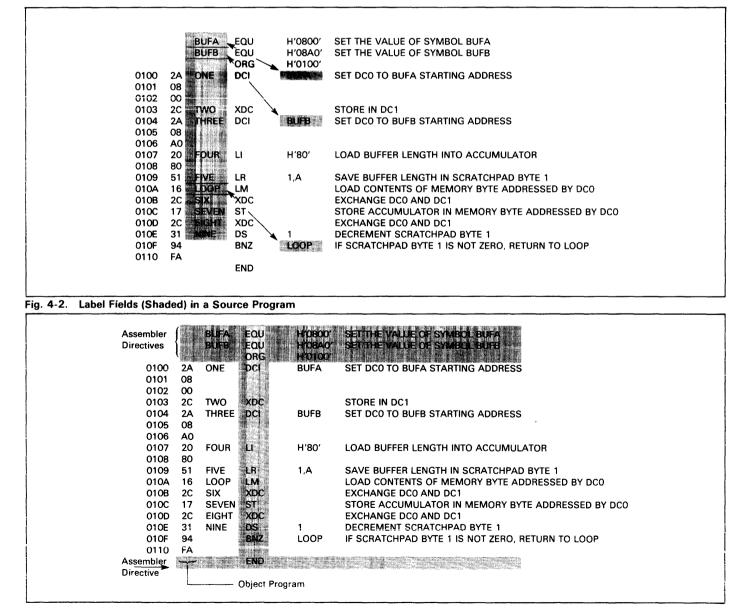

| 4-2                                                         | Label Fields (Shaded) in a Source Program                                                                                                                                                                                                                                                                                                                                                                                                              | 4-2                                                  |

| 4-3                                                         | Mnemonic Field (Vertical Shaded) in a Source Program                                                                                                                                                                                                                                                                                                                                                                                                   | 4-3                                                  |

| 4-4                                                         | Operand Fields (Shaded) in a Source Program                                                                                                                                                                                                                                                                                                                                                                                                            | 4-3                                                  |

| 4-5                                                         | Comment Fields (Shaded) in a Source Program                                                                                                                                                                                                                                                                                                                                                                                                            | 4-3                                                  |

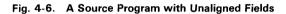

| 4-6                                                         | Source Program with Unaligned Fields                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-3                                                  |

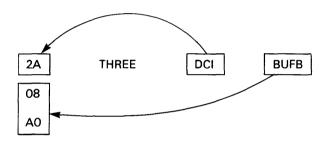

| 4-7                                                         | Symbols in a Source Program                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-5                                                  |

| 5-1                                                         | Assembler Directives (Shaded) in a Source Program                                                                                                                                                                                                                                                                                                                                                                                                      | 5-1                                                  |

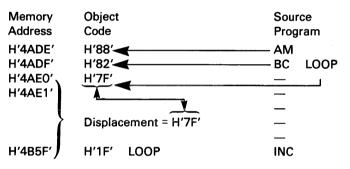

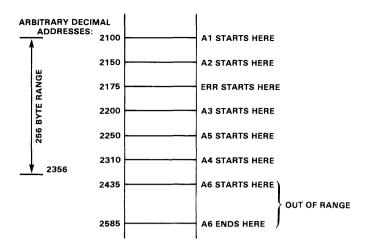

| 6-1                                                         | Generation of a Displacement Object Program Byte in Response to a Forward Branch                                                                                                                                                                                                                                                                                                                                                                       | 6-5                                                  |

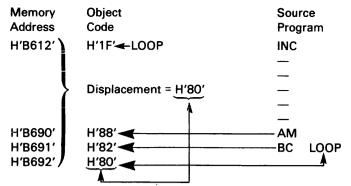

| 6-2                                                         | Generation of a Displacemnt Object Program Byte in Response to a Backward Branch                                                                                                                                                                                                                                                                                                                                                                       | 6-6                                                  |

# TABLE OF CONTENTS (Cont'd)

| FIGURE |                                                              | PAGE |

|--------|--------------------------------------------------------------|------|

| 7-1    | Use of H, Q and DC1 Registers to Hold Three Buffer Addresses | 7-6  |

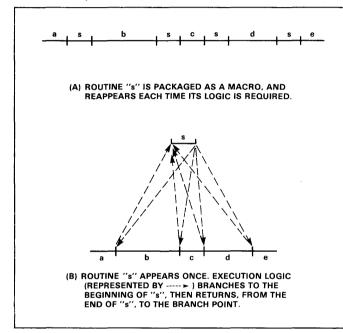

| 7-2    | Subroutine, as Compared to a Macro                           | 7-7  |

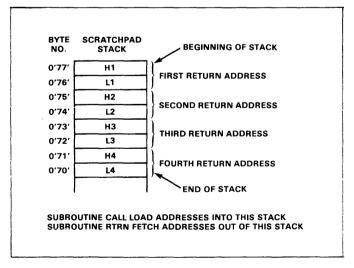

| 7-3    | Scratchpad Stack                                             | 7-10 |

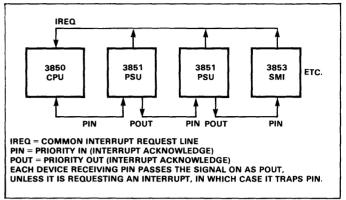

| 8-1    | Daisy Chaining and Interrupt Priority Determination          | 8-4  |

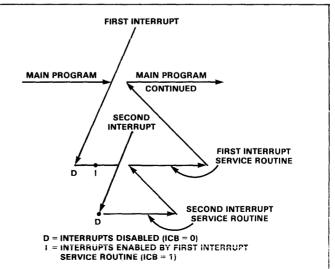

| 8-2    | Two Levels of Interrupt                                      | 8-4  |

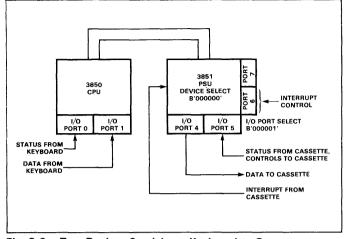

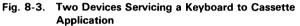

| 8-3    | Two Devices Servicing a Keyboard to Cassette Application     | 8-6  |

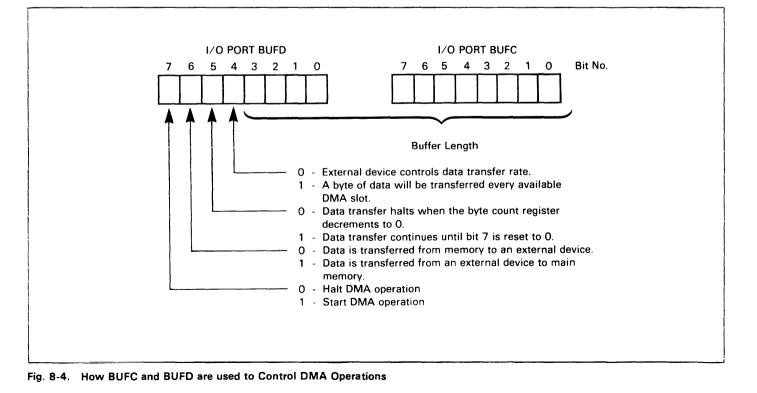

| 8-4    | How BUFC and BUFD are used to Control DMA Operations         | 8-10 |

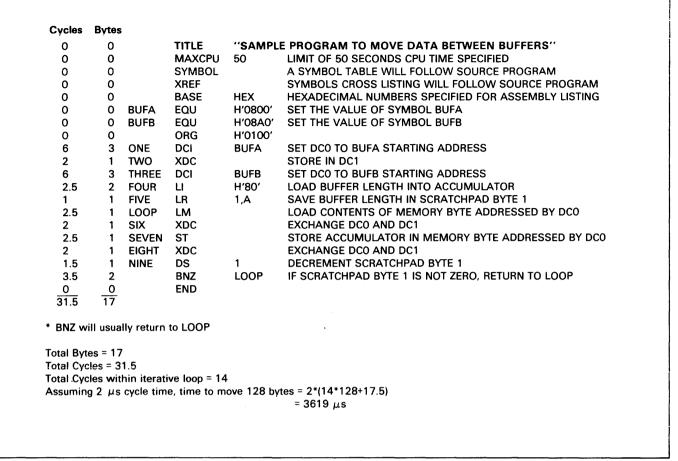

| 9-1    | Counting Cycles and Bytes                                    | 9-2  |

#### LIST OF TABLES

#### TABLE

#### PAGE

| 2-1<br>2-2 | Summary of Status Bits                                              | 2-6<br>2-11 |

|------------|---------------------------------------------------------------------|-------------|

| 4-1        | Summary of Restricted Characters                                    | 4-4         |

| 6-1        | Operand Symbols                                                     | 6-1         |

| 6-2        | Operands Referencing Scratchpad Memory, as Specified by Symbol Sreg | 6-1         |

| 6-3        | Branch Conditions                                                   | 6-6         |

| 6-4        | Branch Conditions for BF Instruction                                | 6-6         |

| 6-5        | Branch Conditions for BT Instruction                                | 6-7         |

| 6-6        | I/O Port Address Assignments                                        | 6-9         |

| 6-7        | LR Instruction Operand Definitions                                  | 6-12        |

| 7-1        | Scratchpad Memory Utilization                                       | 7-1         |

| 7-2        | Use of a Memory Stack for Executing Multiple Level Subroutines      | 7-10        |

| 8-1        | Contents of Interrupt Control I/O Ports                             | 8-4         |

### INTRODUCTION

This manual explains how to write programs for the Fairchild F8 microprocessor system, and how these F8 programs cause a microprocessor system to function as a discrete logic replacement.

The Fairchild F8 family of logic devices consists of a Central Processing Unit and a number of complementary devices, manufactured using n-channel Isoplanar MOS technology. Components of the F8 family include the following devices:

- 1) The 3850 Central Processing Unit (CPU)

- 2) The 3851 Program Storage Unit (PSU)

- 3) The 3852 Dynamic Memory Interface (DMI)

- 4) The 3853 Static Memory Interface (SMI)

- 5) The 3854 Direct Memory Access (DMA)

Complete microprocessor based systems may vary in size and complexity from as little as two devices—the 3850 CPU and the 3851 PSU—to large systems incorporating the above five devices, plus any standard static and/or dynamic Random Access Memory (RAM) devices.

The following are some general characteristics of this microprocessor device set:

- 8-bit data organization

- 2 µs instruction cycle time

- Over 70 microprocessor instructions

- 64 general purpose registers in the CPU

- Binary and decimal arithmetic, and logic functions

- Up to 65,536 bytes of ROM and RAM, in any combination

- No need for special external interface devices

- Internal, programmable real time clocks

- Internal power on and reset logic

- Multi-level interrupt handling

- Clock and timing circuits

#### 1.1 ASSUMED READER BACKGROUND

This manual has been written for logic designers with little or no background in programming.

The reader is assumed to understand the following:

- 1) Binary, octal, binary coded decimal and hexadecimal number systems

- 2) Signed and unsigned binary arithmetic

- 3) Boolean logic

- 4) ASCII and EBCDIC character codes

For readers without the assumed background, a summary of this basic information is given in Appendix A.

#### **1.2 SUPPORTING DOCUMENTATION**

The following manuals provide additional information on the F8 microprocessor:

- 1) F8 Circuit Data Book which provides electrical parameter data for all Fairchild F8 Microprocessor devices.

- 2) F8 Timeshare Operating Systems Manual which explains how to assemble and debug F8 Microprocessor programs on NCSS and GE Timeshare Networks.

- 3) F8 Circuit Reference Manual which describes the interactive timing and signal sequences which occur between devices in the F8 Microprocessor family.

- 4) F8S and F8SEM Users Manuals which describe how to assemble and debug microprocessor programs on the F8S and F8SEM hardware modules.

- 5) F8 Formulator Users and Reference Manuals which describe how to use and maintain Fairchild's F8 Formulator developmental hardware.

## THE F8 MICROPROCESSOR SYSTEM

The purpose of a microprocessor system is to replace discrete logic; but in order to understand why a microprocessor system is effective as a logic design tool, it is first necessary to understand what is in a microprocessor system.

#### 2.1 WHAT IS A MICROPROCESSOR?

After a product has been fabricated using discrete logic components, it consists of one or more logic cards; each card may be visualized as generating a variety of signals output at the card edge, based on signals input at the card edge. The logic devices on the card are specifically selected and sequenced to generate the required product.

If the same product is implemented using the F8 microprocessor, the F8 CPU and its five supporting devices can be made to function in the same way as any one of many millions of different discrete logic device combinations. In other words, the F8 CPU, optionally in conjunction with the supporting devices, has the capacity to duplicate the performance of any discrete logic design, limited only by speed considerations. F8 microprocessor systems have a 2  $\mu$ s instruction cycle time. The functions that will be performed by the F8 microprocessor system are established by a sequence of "instructions", stored in a memory device as a sequence of binary codes. Taken as a whole, the sequence of instructions are referred to as a "stored program".

#### 2.2 SOME BASIC CONCEPTS

Any logic device may be reconstituted from some or all of the following basic functions:

- 1) Binary addition

- 2) The logical operations AND, OR and EXCLUSIVE-OR

- Shifts and rotates of binary digit sequences which are being interpreted as numerical entities (e.g., a byte = eight bits).

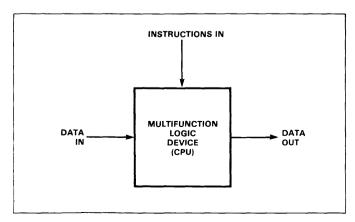

A general purpose logic device can be created by implementing the basic functions listed above on a single chip. If the single chip is to duplicate the performance of other logic devices, it must be provided with a sequence of instructions that enable the required logic in the proper order, plus aa stream of data that is operated on by the specified logic. This is illustrated in Figure 2-1.

Fig. 2-1. Multifunction Logic Device

In order to function, the multifunction logic device will need the following parts:

- A) An Arithmetic Logic Unit (ALU), containing the necessary basic logic functions.

- B) A control unit, which decodes instructions and enables elements of the ALU, as needed.

- C) Registers to hold instruction codes and data, as needed.

- D) Data paths within the CPU, and between the CPU and external devices.

Parts A), B), C), and D) are the basic components of any Central Processing Unit (CPU). A CPU must be the focal point of any computer—maxi, mini or micro.

Referring to Figure 2-1, where do "instructions" and "data in" come from, and where will "data out" go? There are two possibilities: memory or external devices.

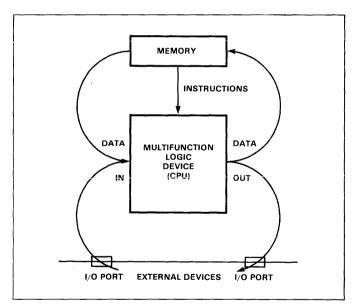

Refer to Figure 2-2. Memory is a passive depository of information where data or instruction codes may be stored. Memory must be divided into individually addressable locations, each of which can store one element of instruction code or one element of data. In an F8 system, each individually addressable location will be an 8-bit data unit (a byte), since the F8 is an 8-bit microprocessor.

Fig. 2-2. Data and Instruction Paths in a Multifunction Logic Device

"External devices" refer to any data source or destination beyond the perimeter of the microprocessor system. Drawing an analogy with a logic card, "external devices" will refer to the world beyond the card edge connector. Data passes between the microprocessor system and external devices via Input/Output (I/O) ports.

#### 2.2.1 Instructions, Programs, Data and Memory

For a microprocessor to perform any specified operation, it will receive and process a sequence of instructions. The sequence may be very long—numbering even into the thousands of instructions. A sequence of instructions that can be taken as a unit is called a program; the purpose of this manual is to describe how a program is constructed out of a sequence of instructions.

Data may (and usually will) be stored in memory. In fact, the 256 possible combinations of eight binary digits (or byte) may represent any of the following types of information:

- 1) An instruction code

- 2) Numeric or address data that is part of an instruction's code

- 3) Numeric or address data that is independent of instruction codes

- 4) A coded representation of a letter of the alphabet, digit or printable character

It would be impossible to determine the content of any memory byte by random inspection. This does not cause problems, since a program will occupy one or more segments of contiguous memory bytes, and data resides in blocks of memory as assigned by the programmer.

#### 2.2.2 Interrupts

The number of programs which may be stored in memory is limited only by the amount of memory available for program storage. If ten programs were stored in memory, by simply identifying one program, the same microprocessor system could be made to function in one of ten different ways.

If a microprocessor has more than one program available for execution, how is the one program which is to be executed identified? There are two separate and distinct ways in which a program may be identified for execution:

- A) Program identification may itself be a programmed function; for example, each program, upon completing execution, may identify the next program to be executed. The key to this method of program identification is that it is internally controlled, within the logic of the microprocessor system.

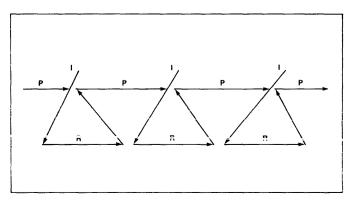

- B) Programs may be called into execution by external devices; this may happen even if another program is in the middle of execution. For example, take the simple case of a microprocessor that is recording data input by an external instrument; while receiving data from the external instrument, the microprocessor performs numerical operations on the collected data. Program executions are illustrated in Figure 2-3.

Fig. 2-3. Program P Being Interrupted to Execute Program R

In Figure 2-3, P represents the program performing numerical operations on the data. Data is collected by repeated execution of program R. Events occur as follows:

- 1) Program P is executing.

- 2) When the external instrument has data which it is ready to transmit, it sends an interrupt signal (I) to the microprocessor, along with the starting address of program R.

- 3) Upon receiving interrupt signal I, the microprocessor does some elementary "housekeeping"; for example, it saves the address of the program P instruction it was about to execute, plus any intermediate data being held in temporary storage registers.

- 4) The microprocessor completely executes program R.

- 5) Upon completion of program R execution, the microprocessor restores values saved in step 3, then continues program P execution from the point where interrupt I occurred. Thus execution of program P appears to have gone into "suspended animation" for the duration of program R execution.

The sequence of events illustrated in Figure 2-3 is quite common in microprocessor applications, and is called an external interrupt. Interrupt programming is described in Section 8.2.

#### 2.2.3 Programmable Clocks

There are many microprocessor applications in which it is important that the microprocessor system be synchronized with the real time of the outside world. Such synchronization is accomplished using programmable clocks, which are registers that count at a known rate. When the shift register counts to zero, the event is marked by an interrupt (as decribed in Section 2.2.2); in this case the interrupt is defined as a "time out" interrupt. Since the rate at which the clock register counts will be known for any microprocessor system, setting a real time interval simply involves loading the register with the correct initial count.

#### 2.2.4 Direct Memory Access

Notice from Figure 2-2 that data may be input to the microprocessor from memory or from an external device, via an I/O port.

It is easy to imagine how, in many applications, data will be transferred from an external device, via an I/O port and the CPU, to memory; the data will then be accessed from memory in the normal course of program execution.

It makes little sense to tie up the logic of the CPU while shunting data from an I/O port to memory; therefore, provisions are made for Direct Memory Access (DMA), whereby data is moved between memory and an "I/O port", bypassing the CPU entirely. The DMA "I/O port" is called a "DMA channel".

In order to implement DMA, the microprocessor system must have logic (outside the CPU) which provides the following three pieces of information:

- 1) A starting memory address for a data block.

- 2) A byte length for the data block.

- 3) The direction of the data movement.

If the microprocessor has this logic, data may be transferred between memory and an I/O port independent of, and in parallel with, unrelated CPU-memory operations.

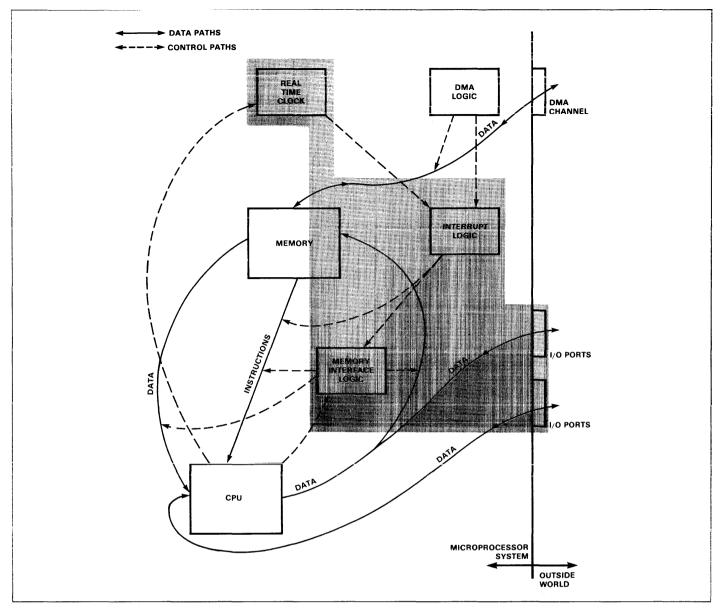

#### 2.2.5 A Complete Microprocessor System

To summarize, a complete microprocessor system will have the following logical components:

- 1) A CPU, which is the multifunction logic device of the system.

- 2) Memory (of various types and combinations), in which programs and data are stored.

- 3) Memory interface logic which identifies:

- a) the next memory location which must be accessed to fetch instruction codes for the CPU, and

- b) the memory location from which a byte of data will be read, or to which a byte of data will be written.

- I/O ports, through which bidirectional data passes between the microprocessor system and external devices.

- 5) DMA logic, which provides a direct data path between memory and external devices, bypassing the CPU.

- 6) Interrupt logic, which causes the CPU to temporarily suspend current program execution. Along with each interrupt request signal, interrupt logic identifies the program which is to implement operations required by the source of the interrupt.

- Real time clock logic, which synchronizes the entire microprocessor system with the real outside world by generating interrupts at variably definable time intervals.

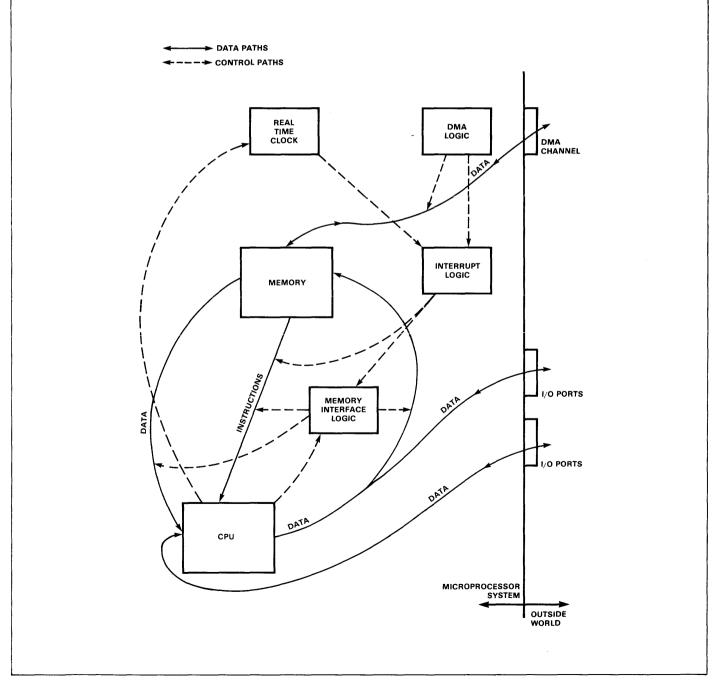

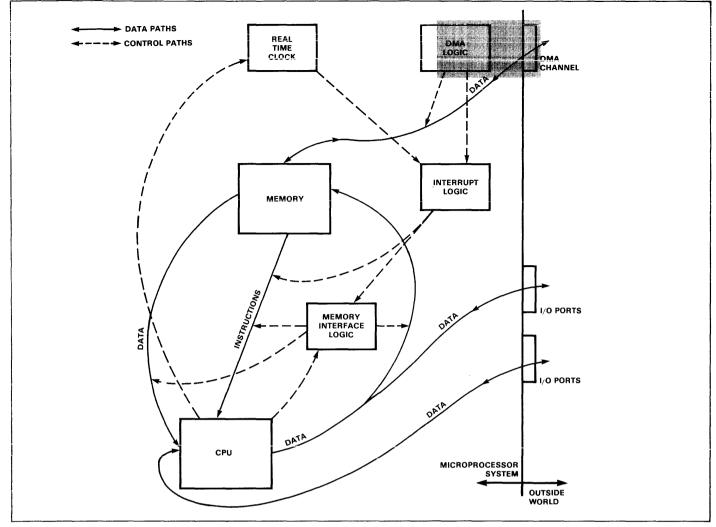

Figure 2-4 illustrates these seven logical components, with associated data flow paths.

Fig. 2-4. Logical Components, Data Paths and Control Paths in any Microprocessor System

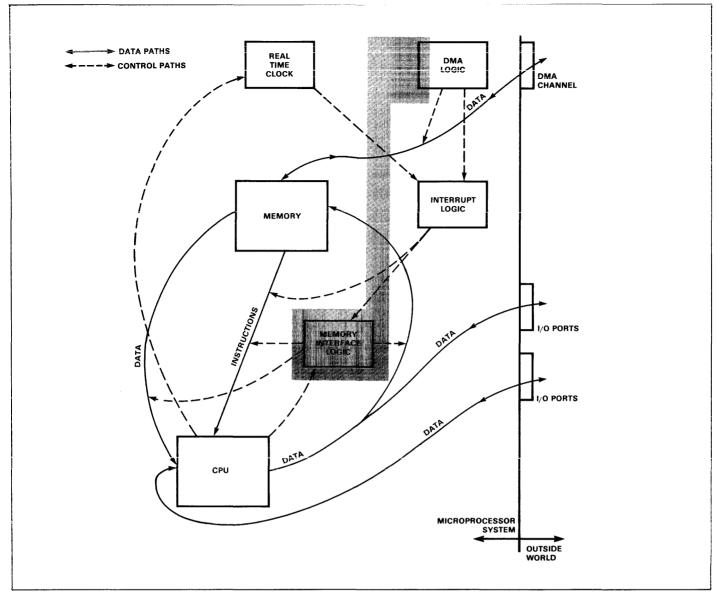

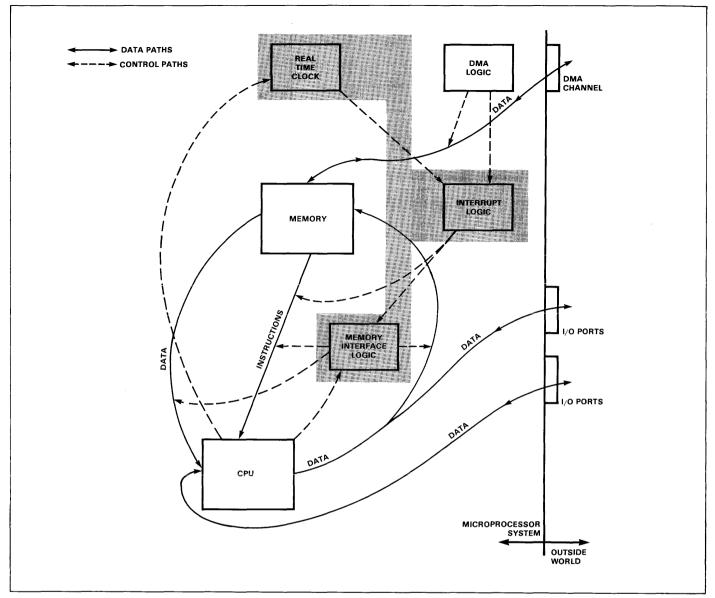

#### 2.3 THE F8 SYSTEM

There is no one-for-one correspondence between the logical components of a microprocessor system, as illustrated in Figure 2-4, and the devices of the F8, or any other microprocessor product. In fact, it is counter-productive to extend the concept of isolating functions on separate devices because it reduces the flexibility of a microprocessor system to satisfy simple, as well as complex, applications needs. More than any other microprocessor product, the F8 combines many functions on single chips, thus allowing simple systems to be implemented with as few as two devices, and complex systems to be implemented using many devices.

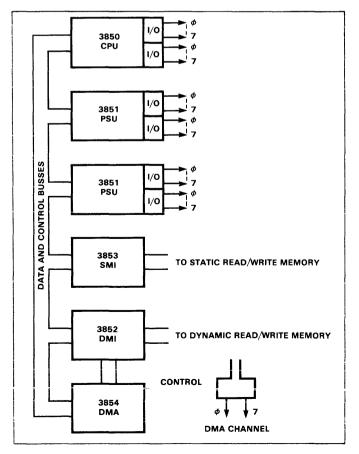

Figure 2-5 illustrates the way in which F8 microprocessor system devices interconnect to give a variety of system configurations.

The simplest F8 system contains one 3850 CPU and one 3851 PSU.

Another very simple F8 system consists of one 3850 CPU, plus either one 3852 DMI interfaced to a single dynamic memory, or one 3853 SMI interfaced to a single static memory device.

A fully expanded F8 system may have one 3850 CPU, one 3852 DMI and one 3853 SMI device, up to four 3854 DMA devices, plus 3851 PSU and static or dynamic memory devices in any combination, providing not more than a combined total of 65,536 bytes of memory are directly addressed by the 3850 CPU. It is possible to address more than 65,536 bytes of memory using special techniques which are described in the F8 Circuit Reference Manual.

#### Fig. 2-5. F8 Microprocessor System Configurations

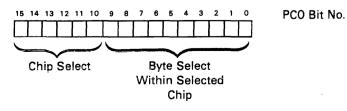

#### 2.3.1 Chip and I/O Port Selection

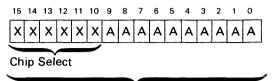

Every 3851 PSU has two permanent select codes—a chip select code and an I/O port select code.

The 3851 PSU chip select code is a six digit binary number, which is always the highest six bits for memory addresses on that device:

Memory Address for Individual Bytes on Chip

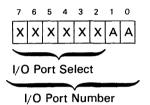

The 3851 PSU I/O port select code is also a six digit binary number, and is independent of the chip select code. The I/O port select code is always the highest six bits for I/O port numbers on that device:

The 3852 DMI and 3853 SMI devices have a fixed (preassigned) I/O port select code, but have no on-board chip select code.

The dynamic and/or static memories associated with the 3852 DMI and 3853 SMI derive their select function from external logic. This allows the system designer complete freedom with respect to memory space partitioning.

Every F8 microprocessor system must have one memory device whose byte addresses start at 0; the first instruction executed when an F8 system is powered up is the instruction stored in memory byte 0.

#### 2.4 THE 3850 CPU

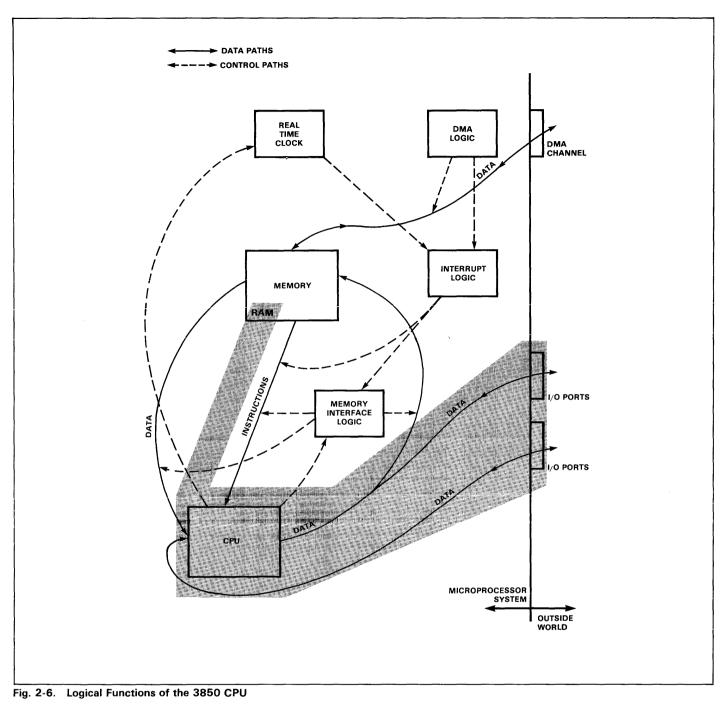

Figure 2-6 illustrates the logical functions implemented on the 3850 CPU.

The heart of the F8 microprocessor system is the 3850 CPU, which contains data manipulation logic in an Arithmetic Logic Unit (ALU). Eight-bit instruction codes are decoded by a Control Unit (CU), which controls execution of logic internal to the 3850 CPU and generates signals controlling operations of other devices in the system.

#### 2.4.1 Timing

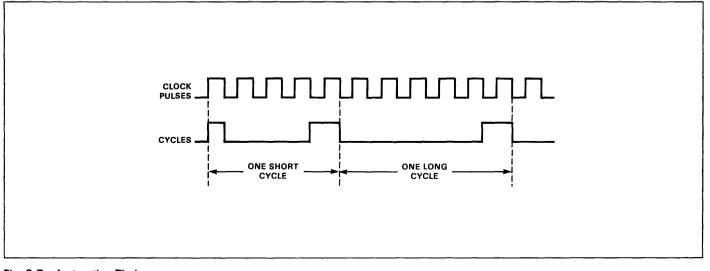

System timing is illustrated in Figure 2-7. System timing is controlled by an external or internal clock, which provides clock pulses of not less than 500 ns and not more than  $10\mu$ s. In response to instruction codes, the CPU creates instruction timing cycles of either 4 or 6 clock pulses. The fastest instruction will execute in one short (4 clock pulse) cycle; the slowest instruction will execute in one short (4 clock pulse) cycle plus three long (6 clock pulse) cycles.

Fig. 2-7. Instruction Timing

#### 2.4.2 CPU Registers

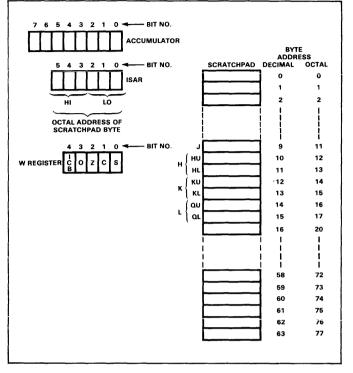

The 3850 CPU has an 8-bit Accumulator Register and a Scratchpad consisting of 64 8-bit registers. In addition there is a 6-bit Indirect Scratchpad Address Register (ISAR), which is used to address the scratchpad and a 5-bit Status Register (the W register), which identifies selected status conditions associated with the results of CPU operations. Figure 2-8 illustrates the CPU register.

Fig. 2-8. 3850 CPU Programmable Registers

Data in the Accumulator may be manipulated by the ALU. Individual instructions allow the contents of the Accumulator to be operated on in a variety of ways. Data may be transferred between the Accumulator and other CPU registers, or between the Accumulator and data locations outside the CPU.

The Scratchpad is the principal depository of frequently accescessed data and, in small microprocessor configurations, may represent the system's only Read/Write Memory. Because the Scratchpad actually resides on the CPU, instructions that reference Scratchpad bytes execute in one short cycle; these are the fastest executing F8 instructions.

The first 16 Scratchpad bytes can be identified by instructions without using the ISAR. The remaining Scratchpad bytes are referenced via the ISAR; i.e., the ISAR is assumed to hold the address of the Scratchpad byte which is to be referenced. Observe that the first 16 bytes of the Scratchpad can also be referenced via the ISAR.

The ISAR should be visualized as holding two octal digits, HI and LO. This division of the ISAR is important, since a number of instructions increment or decrement the contents of the ISAR when referencing Scratchpad bytes via the ISAR. This allows a sequence of contiguous scratchpad bytes to be easily referenced. However, only the low order octal digit (LO) is incremented or decremented; thus ISAR is incremented from 0'27' to 0'20', not to 0'30'. Similarly, ISAR is decremented

from 0'20' to 0'27', not to 0'17'. This feature of the iSAR greatly simplifies many program sequences, as will be described in Section 7.

Seven of the Scratchpad registers (9 through 15) have special significance. Data from register 9 may be moved directly between register 9 and the W register, bypassing the Accumulator. Registers 10 through 15 are connected to memory interface logic, as described in Sections 2.5, 2.6 and 2.7.

#### 2.4.3 Status

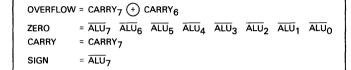

A number of operations performed by the Arithmetic Logic Unit (ALU) generate results, selected characteristics of which are important to logic sequences. Table 2-1 summarizes the W register status bits, which are individually described next.

Table 2-1.

A Summary of Status Bits

#### SIGN

When the results of an ALU operation are being interpreted as a signed binary number, the high order bit (bit 7) represents the sign of the number (see Appendix A). At the conclusion of instructions that may modify the Accumulator bit 7, the S bit (W register bit 0) is set to the complement of the Accumulator bit 7.

#### CARRY

The C bit (W register bit 1) may be visualized as an extension of an 8-bit data unit; i.e., bit 8 of a 9-bit data unit. When two bytes are added and the sum is greater than 255, the carry out of bit 7 appears in the C bit. Here are some examples:

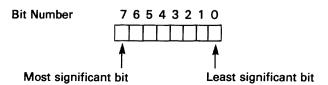

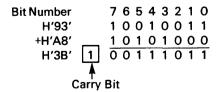

| С                     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0- Bit Number |

|-----------------------|---|---|---|---|---|---|---|---------------|

| Accumulator contents: | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1             |

| Value added:          | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0             |

| Sum: 0                | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1             |

There is no carry, so C is reset to 0.

| C                     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0- Bit Number |

|-----------------------|---|---|---|---|---|---|---|---------------|

| Accumulator contents: | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1             |

| Value added:          | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1             |

| Sum: 1                | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0             |

There is a carry, so C is set to 1.

#### ZERO

The Z bit (W Register bit 2) is set whenever an arithmetic or logical operation generates a zero result. The Z bit is reset to 0 when an arithmetic or logical operation could have generated a zero result, but did not.

Load instructions do not affect status bits.

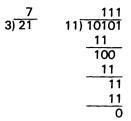

a) The Accumulator contains 01101011. The value 00010101 is added to the Accumulator:

| Accumulator contents: | 01101011 |

|-----------------------|----------|

| Value added:          | 00010101 |

| Sum:                  | 10000000 |

The result in the Accumulator is not zero, so the Z bit is reset to 0. (There is no carry, so C is reset to 0).

b) Next, the Accumulator contents are shifted left one bit position:

Since the result in the Accumulator is now zero, the Z bit is set to 1.

c) Subsequently the value 1101111 is loaded into the Accumulator. Even though the Accumulator no longer contains zero, the Z bit remains set at 1 since an Accumulator load is neither an arithmetic nor a logical operation, therefore has no effect on the Z bit.

#### OVERFLOW

The high order Accumulator bit (bit 7) represents the sign of the number. When the Accumulator contents are being interpreted as a signed binary number, some method must be provided for indicating carries out of the highest numeric bit (bit 6 of the Accumulator). This is done using the O bit (W register bit 3). After arithmetic operations, the O bit is set to the EXCLUSIVE-OR of Carry Out of bits 6 and bits 7. This simplifies signed binary arithmetic as shown in Section 10.3 and in Appendix A. Here are some examples:

| (                     | С | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Bit Number |

|-----------------------|---|---|---|---|---|---|---|---|---|------------|

| Accumulator contents: |   | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |            |

| Value added:          |   | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |            |

| Sum:                  | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |            |

There is a carry out of bit 6 and out of bit 7, so the O bit is reset to 0 ( $1 \oplus 1 = 0$ ). The C bit is set to 1.

| С                     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Bit Number |

|-----------------------|---|---|---|---|---|---|---|---|------------|

| Accumulator contents: | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |            |

| Value added:          | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |            |

| Sum: 0                | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |            |

There is a carry out of bit 6, but no carry out of bit 7; the O bit is set to 1  $(1 \oplus 0 = 1)$ . The C bit is reset to 0.

When the Overflow bit is set, the magnitude of the number is too large for the 7-bit numeric field within the byte, and the sign bit has been destroyed. However, the 9-bit field made up of the Carry bit (high order) and the data byte give a valid 9-bit signed binary result.

#### **ICB AND INTERRUPTS**

External logic can alter the operations sequence within the CPU by interrupting ongoing operations, as described in Section 2.2.2. However, interrupts are allowed only when the ICB bit (W register bit 4) is set to 1; interrupts are disallowed when the ICB bit is reset to 0.

#### 2.4.4 3850 Input/Output

The 3850 CPU communicates with the outside world in two ways:

To execute instructions, instruction codes must be input from the external storage device (probably a 3851 PSU) where they are being maintained. Data stored in a memory device may have to be loaded into the CPU in order to meet the requirements of the instruction being executed. This type of communication between the 3850 CPU and the outside world is of no immediate concern to an F8 programmer, since it involves data flows within the confines of the microprocessor system, and requires no special considerations beyond an understanding of instruction execution sequences.

Input/output programming, as the term is commonly used, refers to data transfers between the microprocessor system and logic beyond the microprocessor system. The 3850 CPU has two 8-bit, bidirectional ports, via which 8-bit parallel data may be transferred in either direction, between the 3850 CPU and logic external to the microprocessor system. The two 3850 CPU I/O ports are identified by the hexadecimal port addresses H'00' and H'01'.

#### 2.5 THE 3851 PSU

Figure 2-9 illustrates the logical functions implemented on the 3851 PSU.

The 3851 PSU provides an F8 microprocessor system with 1024 bytes of Read Only Memory. 3851 memory is usually used to store instructions, but may also be used to store data that is read, but never altered. In addition, each 3851 PSU provides two 8-bit I/O ports, a programmable timer and external interrupt processing logic.

The 3851 PSU is the logic device which is modified and replaced to reflect a product's continuing engineering and field upgrades.

In microprocessor systems, instruction codes are usually stored in a PSU to prevent accidental erasure. As many as 64 3851 PSU's may be connected to one 3850 CPU, yet a single 3851 PSU interfaced to a 3850 CPU, provides a viable microprocessor system with the following capacities:

- 1024 bytes of program storage (on the 3851)

- 64 bytes of Read/Write Memory (on the 3850)

- 4 separately addressable, bidirectional I/O ports (2 on the 3850, 2 on the 3851)

- An external interrupt line

- A programmable clock

#### 2.5.1 3851 Timing

Timing signals created by the 3850 CPU, and illustrated in Figure 2-7, control operation sequences in the 3851 PSU.

Fig. 2-9. Logical Functions of the 3851 PSU

#### 2.5.2 3851 Registers

In addition to 1024 bytes of ROM, the 3851 contains three 16-bit address registers, which are described next.

#### **PROGRAM COUNTER (PCO)**

This 16-bit register provides the address of the memory byte from which the next instruction code will be fetched for transmittal to the 3850 CPU. After each byte of instruction code is fetched, logic internal to the 3851 increments the contents of PCO to address the next memory byte.

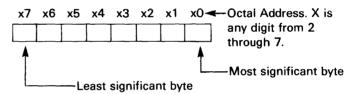

Even though each 3851 PSU contains only 1024 bytes of memory, PCO preserves a 16-bit memory address. Thus PCO may be interpreted as follows:

Each 3851 device has a unique select code that is a permanent mask option; 3851 memory access logic is only activated when the six Chip Select bits of PCO match the 3851 select code. Thus, if more than one 3851 is present in an F8 system, every 3851 device's PCO register holds the address of the memory byte from which the next instruction code will be fetched for transmittal to the 3850 CPU; but an instruction fetch will actually be executed from one 3851 device only.

The PCO registers of the 3851 devices are logically connected to 3850 scratchpad bytes 12 and 13, designated as the K register, and bytes 14 and 15, designated as the Q register in Figure 2-8. Specific instructions allow the contents of the K or Q register to be loaded into every PCO register. Specific instructions allow the PCO registers' contents to be modified in order to control microprocessor logic sequences.

Note that in a correctly designed F8 microprocessor system, when there is more than one 3851 device, every PC0 register will always contain exactly the same address.

#### STACK REGISTER (PC1)

Every 3851 device has a 16-bit Stack Register, which is a buffer for the contents of PCO. This allows program execution sequence to be modified by changing the PCO registers' contents, while the previous contents of PCO are saved in PC1; thus programs may return to the prior instruction execution sequence.

The PC1 registers are logically connected to the 3850 scratchpad bytes 12 and 13, designated as the K register in Figure 2-8. Specific instructions allow the contents of the K register to be loaded into every PC1 register, or the PC1 registers' contents to be loaded into the K register.

#### DATA COUNTER (DC)

Every 3851 device has a 16-bit Data Counter register which contains the address of the memory byte (external to the 3850 CPU) from which data is to be accessed. For example, an instruction requiring a data byte to be loaded from external memory into the 3850 Accumulator will fetch the contents of the data byte addressed by the DC registers.

The DC registers are 16-bit registers, where the high order six bits (bits 15 to 10) are interpreted as chip select bits, and the low order nine bits (bits 9 to 0) provide the byte address.

The DCO registers are logically linked to the H and Q registers in the same way that the PC1 registers are logically linked to scratchpad register K.

#### 2.5.3 3851 Input/Output

Each 3851 PSU has two bidirectional, 8-bit I/O ports. Each port's address, using binary notation, is XXXXX00 or XXXXX01, where the X binary digits are the device's unique I/O port select code. Note that every 3851 PSU has an I/O port select code and an independent chip select code.

#### 2.5.4 3851 Local Timer and Interrupt

3851 programmable timer and interrupt logic are accessed via the binary port addresses XXXXXX11 and XXXXX10, respectively; the X binary digits are the I/O port select codes described in Section 2.5.3.

The programmable timer port is a polynomial shift register which runs continuously, sending a signal to the interrupt control logic whenever the timer count equals zero.

Any numeric value between 0 and 255 may be loaded into the programmable timer port by an appropriate instruction code. If 255 (hexadecimal FF) is loaded into a timer port, the timer is stopped. Any other value loaded into a timer port is decremented once every 31 clock pulses (see Figure 2-7); therefore delays up to 7905 clock pulses may be programmed.

The local interrupt port is loaded by an appropriate instruction, with a control code; bits 0 and 1 of the control code are interpreted as follows:

| Bit 1 | Bit O | Function                   |

|-------|-------|----------------------------|

| 0     | 0     | Disallow all interrupts    |

| 0     | 1     | Enable external interrupts |

| 1     | 0     | Disallow all interrupts    |

| 1     | 1     | Enable timer interrupts;   |

If timer interrupts have been enabled and if the 3850 CPU has enabled interrupts (via the ICB status), then when the local timer decrements to 0, an interrupt request is transmitted to the 3850 CPU.

The way in which the local timer and interrupt ports are used is described in Section 8.3.

#### 2.6 THE 3852 DYNAMIC MEMORY INTERFACE

Figure 2-10 illustrates the logical functions implemented on the 3852 DMI device.

The 3852 DMI device interfaces dynamic random access memory (e.g., Fairchild 3540 RAM) to a 3850 CPU. One 3852 DMI device interfaces up to 65,536 bytes of RAM memory to the 3850 CPU. However, recall that a combined maximum of 65,536 bytes of ROM and RAM may be addressed by the 3850 CPU unless special additional memory interfacing logic is added to the microprocessor system.

Only one 3852 DMI device will normally be present in an F8 microprocessor system.

The 3854 DMA device may be attached to the 3852 DMI device enabling data to be transferred between memory devices and any external device, bypassing the 3850 CPU.

#### 2.6.1 3852 Timing

Timing signals created by the 3850 CPU, and illustrated in Figure 2-7, control operation sequences in the 3852 DMI.

#### 2.6.2 3852 Registers

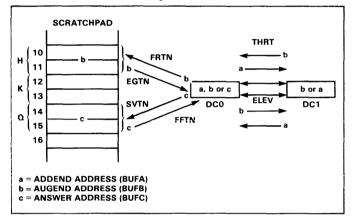

The 3852 DMI device has the same address registers as the 3851 PSU; however, the 3852 DMI has two Data Counter registers. Thus the 3852 has one Program Counter (PC0), one Stack Pointer (PC1) and two Data Counters (DC0 and DC1).